Verilog 16位超前进位加法器源码

”16_bit_cla_verilog 16位加法器“ 的搜索结果

这个zip包包含三个项目文件,分别是数据运算定点加法器、4bit超前进位加法器、使用4bit CLA 组合设计的一个 16bit 加法器。

提供关于 BCD 加法器的结果和模拟过程进行说明(Verilog源代码,输出示例,详细描述过程)。

4bit超前进位加法器(CLA)源代码,用组合逻辑实现

在Verilog中,可以使用以下代码来实现4位cla加法器: module cla_adder_4bit( input [3:0] A, // 输入A,4位二进制数 input [3:0] B, // 输入B,4位二进制数 output [3:0] Sum, // 输出Sum,4位二进制数的和 output...

这里把一个4位全加器当做一个1bit的来用,4个连在一起,通过一个cla_4实现超前进位。

verilog 超前进位加法器

Verilog语言编写32位并行加法器的理解 近日,为了完成本学期的计算机组成原理课程大作业的要求,我开始学习利用verilog语言编写的一套32位并行加法器以完成在整个项目中提高运算速度的基本要求。考虑到verilog语言和...

verilog加法器学习笔记,配合hdlbits例题(半加器、全加器、等波纹加法器、进位选择加法器、超前进位加法器)

一,内容介绍 加法器是数字电路中的最基础电路之一,也是CPU的核心功能之一。 在这个专栏,我会把所有我知道的数字电路的加法器相关模型...上一篇:4位行波加法器设计 目前:四位超前进位加法器设计 下一篇:暂无 ...

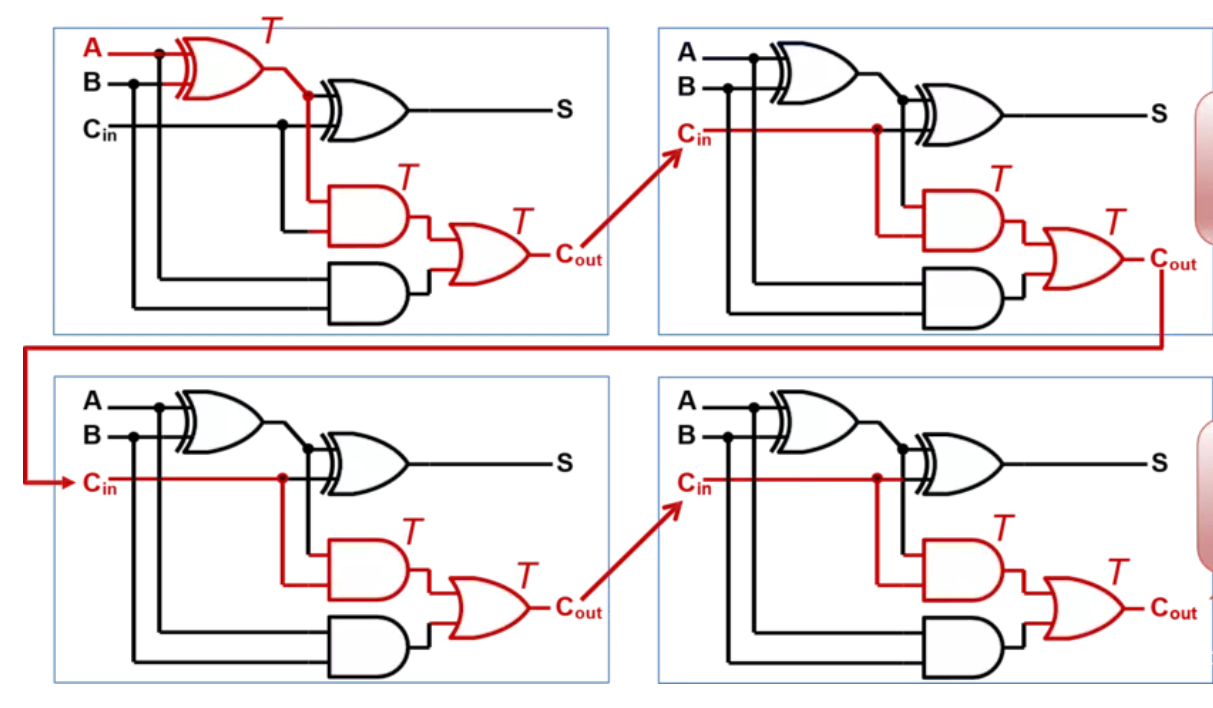

1. 行波进位实现方式:

Verilog,我可以为始终块内的多个位分配一个位值(Verilog, can i assign a bit value to multiple bits inside always block)以下是代码:always @ (C[n-1])beginC[2*n-1:n]=C[n-1];end那可能吗? 如果没有,我该...

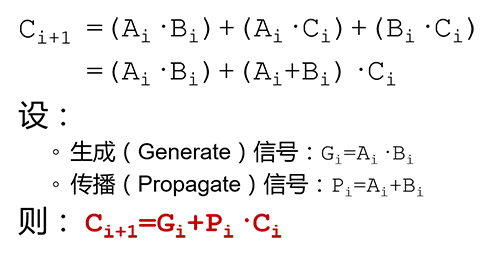

将64位输入分解为16组4位的超前进位加法器,第一级得到得到的16组为超前进位的第二级,该级组间仍然使用超前进位的逻辑进行实现,可以进一步再分为4组,形成第三级。由于行波进位加法器具有明显的延迟,从图中可以...

测试在实现半加器和全加器的基础上开始实现多位数的加法器。

算术逻辑单元是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由"And Gate"(与门) 和"Or Gate"(或门)构成的算术逻辑单元,主要功能是进行二位元的算术运算,如加减乘(不包括整数除法)。...

全加器是指对输入的两个二进制数相加(A与B)同时会输入一个低位传来的进位(Ci-1),...一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

1.条件语句(if_else语句)3钟形式的if语句:1)if(表达式)语句。如if(a>b)out1 = int1;2)if(表达式)语句;else语句;如if(a>b)out1 = int1;elseout1 = int2;3)if(表达式1)语句1;else if(表达式2) 语句2;...

module adder_CLA32( input wire [31:0] a_in , b_in , input wire c_in , output wire [31:0] sum_o, output wire c_o ); wire [8:0] c; assign c[0] = c_in; assign c_o = c[8]; generate genvar i;.

推荐文章

- c语言链表查找成绩不及格,【查找链表面试题】面试问题:C语言学生成绩… - 看准网...-程序员宅基地

- 计算机网络:20 网络应用需求_应用对网络需求-程序员宅基地

- BEVFusion论文解读-程序员宅基地

- multisim怎么设置晶体管rbe_山东大学 模电实验 实验一:单极放大器 - 图文 --程序员宅基地

- 华为OD机试真题-灰度图恢复-2023年OD统一考试(C卷)-程序员宅基地

- 【机器学习】(周志华--西瓜书) 真正例率(TPR)、假正例率(FPR)与查准率(P)、查全率(R)_真正例率和假正例率,查准率,查全率,概念,区别,联系-程序员宅基地

- Python Django 版本对应表以及Mysql对应版本_django版本和mysql对应关系-程序员宅基地

- Maven的pom.xml文件结构之基本配置packaging和多模块聚合结构_pom <packaging>-程序员宅基地

- Composer 原理(二) -- 小丑_composer repositories-程序员宅基地

- W5500+F4官网TCPClient代码出现IP读取有问题,乱码问题_w5500 ping 网络助手 乱码 send(sock_tcps,tcp_server_buff,-程序员宅基地